# **MEMS Fuze-on-a-Chip**

- Low-Cost Fuzes

- Scalable Production Process

- Enormous Silicon Manufacturing Infrastructure

- Navy: Design, Prototype, Pilot Production

- Army: Explosive Train

- MicroAssembly/Laserlith: FEA, Packaging and Integration, Production

- Stresau Laboratory: Loading, Testing

- Progress

- Low-Temperature Wafer Scale Packaging

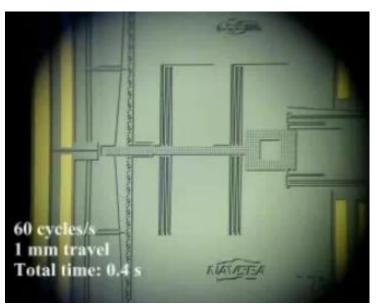

- Fabrication Iterations of Navy S&A Design

- High-G Results of Navy S&A Design

## MicroAssembly

- Operating since 1998

- Partnership

- Navy S&A Design

- Army EDF-11 Integration

- Room-Temperature Hermetic Sealing Process Compatible with Energetic Materials

- Technology Transition

- New MEMS Manufacturing Cleanroom

- Loading and Packaging Facility for Volume Production

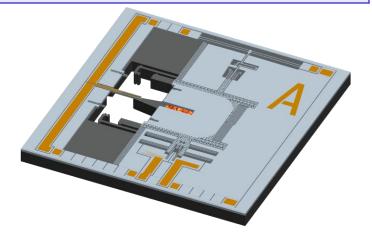

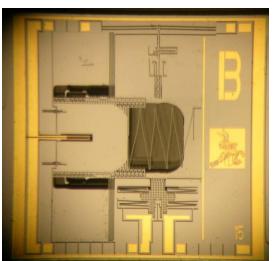

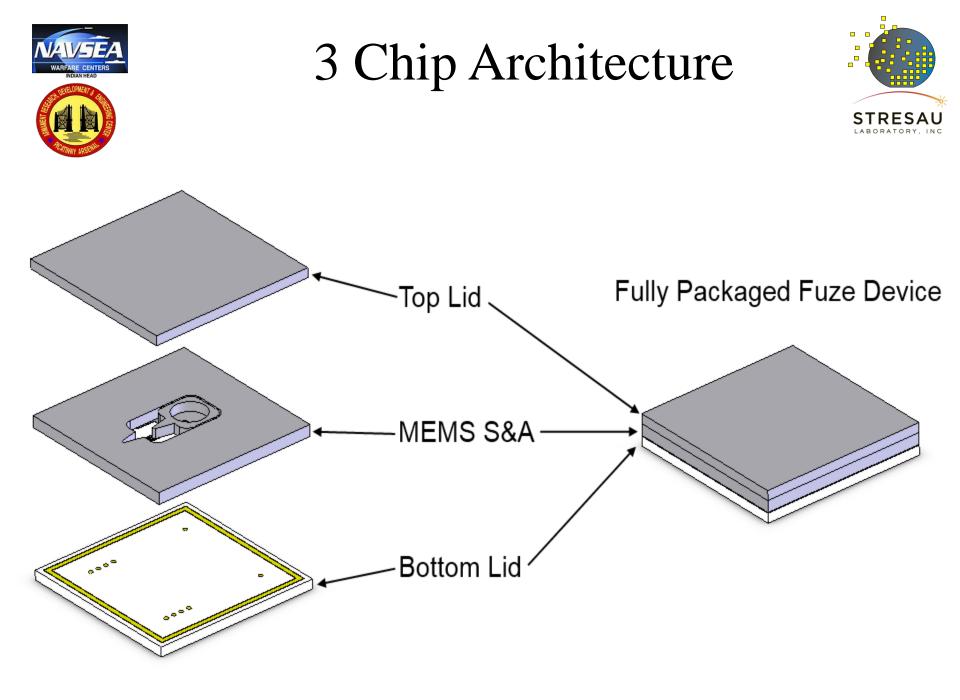

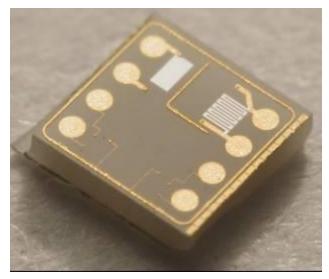

# Fabrication of Navy S&A Design

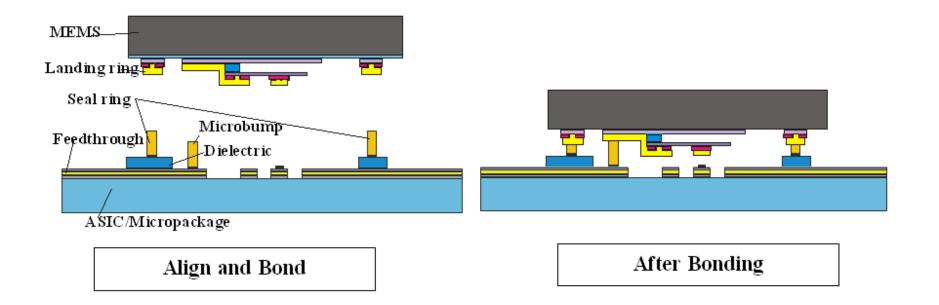

- Packaging

- Cost and Capacity

- Manufacturing

- Next Steps

# Fuze Approaches

| Approach           | Safe & Arm               | Hermetic Packaging<br>for Long Shelf Life |

|--------------------|--------------------------|-------------------------------------------|

| Traditional        | Watchmaker               | One at a Time                             |

| Navy/MicroAssembly | COTS Silicon DRIE        | Batch                                     |

| Other Approaches   | LIGA<br>Multilayer Metal | One at a Time                             |

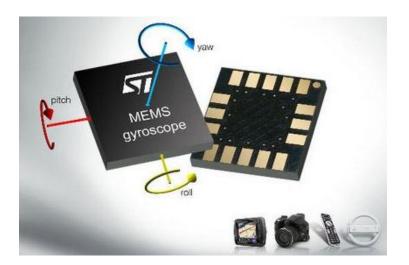

### COTS Silicon Safe & Arm

- Enabler: COTS Deep Reactive Ion Etcher (DRIE)

- Driver: MEMS Gyroscopes

- Industry Base

- At Least 1 COTS DRIE Etcher per Foundry

- Team Owns 2 Etchers

- MEMS Gyroscopes

- Millions of Units per Year

- Cell phones, Automotive Stability

- InvenSense, Seiko Epson, STMicroelectronics, Analog Devices

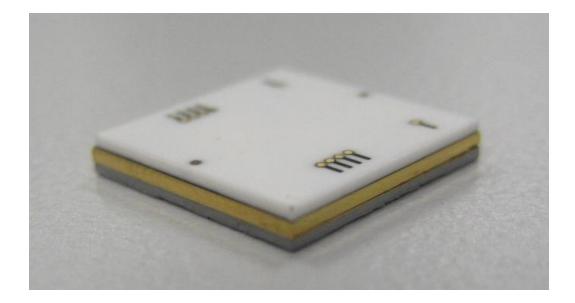

Key Milestone

#### Hermetically Packaged MEMS S&A With Scalable Packaging Process

## Outline

- Fabrication of Navy S&A Design

- Packaging

- Cost and Capacity

- Manufacturing Facility

- Next Steps

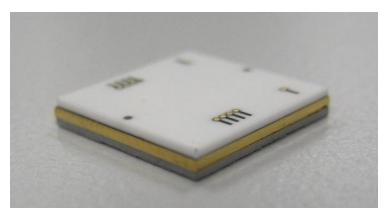

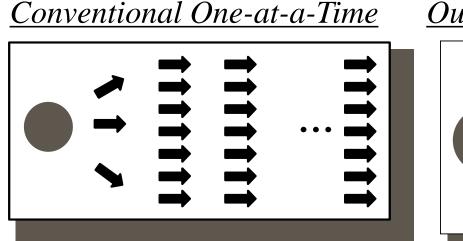

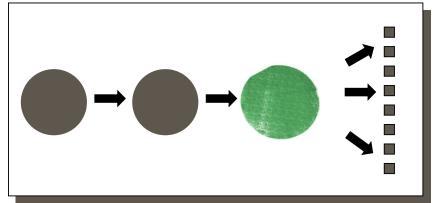

# Low Cost Wafer Level Package

- Packaging is Expensive

- Each Part Must Undergo Many Steps

- Unique Capability

- Compatible with Energetic Materials

- One Hundred Steps Instead of Tens of Thousands

- Yield >90%: Reduce Cost by >10X

Our Solution: Thousands-at-a Time

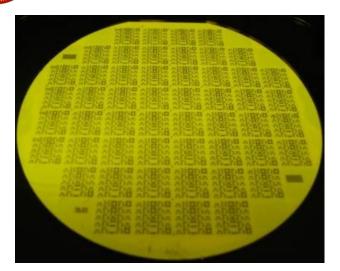

# 2-Substrate MEMS Process

#### Used in Many Device Designs

- >90% Yield

- Integrated Hermetic Packaging

- Eliminates >80% of Production Cost

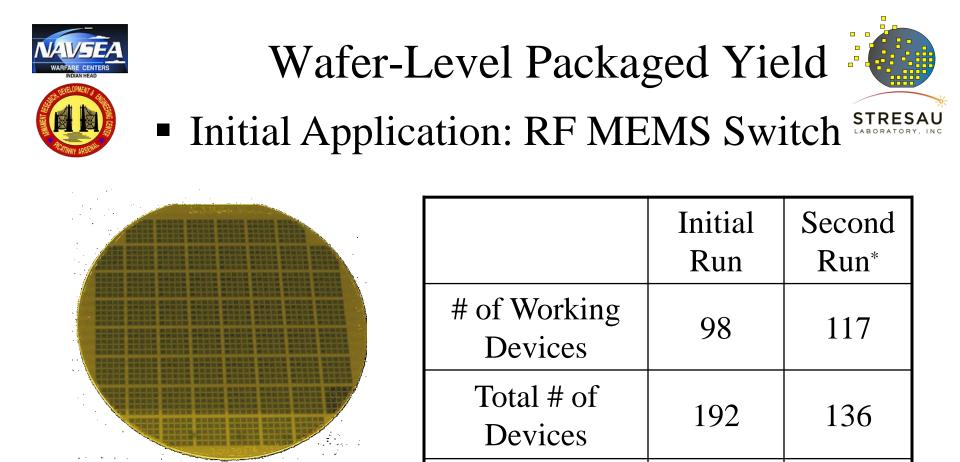

**Overall Yield**\*

\*Process improvements were made and a second run was performed 3 months after the initial run.

51%

86%

## Hermetic Packaging Yield

| # of Hermetic<br>Packages | 45  |

|---------------------------|-----|

| Total # of<br>Packages    | 50  |

| Yield                     | 90% |

## Outline

- Fabrication of Navy S&A Design

- Packaging

- Cost and Capacity

- Manufacturing Facility

- Next Steps

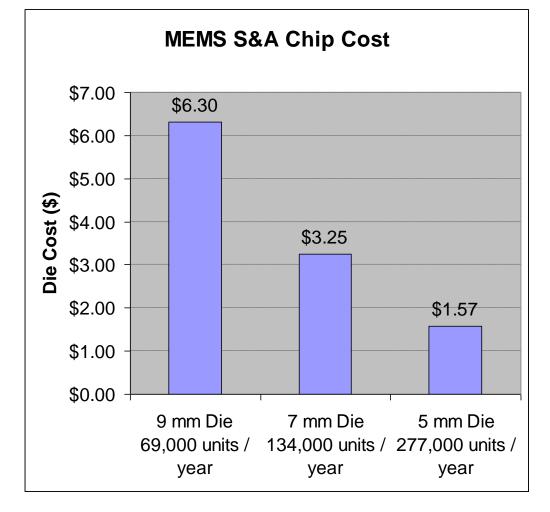

## Processing Cost Estimate

#### • Navy Cost Estimate

- 500 Wafers per Year

- 6" Wafer Size (MEMS Fab)

- Small Scale

Production

- Goal: <u>\$30 each</u>

- 4" Pilot Line Q4 2010 45,000/year

- 3 Wafers/Day (1 shift)

- 300 Days/Yr

- 250 Devices/Wafer (4" wafers)

- Simple 6" Manufacturing Line: 675,000/year

- 9 Wafers/Day (3 shifts)

- 300 Days/Yr

- 250 Devices/Wafer (6" wafers)

- Wafer bonder needs to be upgraded to 6"

- Fabrication of Navy S&A Design

- Packaging

- Cost and Capacity

- Manufacturing Facility

- Next Steps

# MEMS Production Cleanroom

- Cleanroom Qualified

- Equipment Set

- DRIE Etch (4", 6')

- Metallization (4", 6")

- Lithography (4", 6")

- Resist Coating (4", 6")

- Resist Developing (4", 6")

- Wafer Bonding (4"): 6" to be built

- Dicing (4" and 6")

- Fabrication of Navy S&A Design

- Packaging

- Cost and Capacity

- Manufacturing Facility

- Next Steps

Next Steps

#### Low Cost Scalable Production

- Wafer-Scale 6" Ramp-Up

- Fuze Development

- DoD Gun Tests

- Explosive Train and Flyer

- Battery/Power, G-Sensors, Control, ...