Non-technical per ITAR 120.10(5)

AIR

SEA

LAND

SPACE

CYBER

### Sustainment and Upgrades of Legacy Systems

### How to Address Scope and Cost Risk for Obsolescence Upgrades

Milly Lierman and Tim Morrill Engineering Fellows Raytheon Missile Systems 24 October 2012

This presentation contains no technical data as defined under ITAR 120.10.

## How to Address Scope and Cost Risk for Obsolescence Upgrades

- "It's just a simple upgrade" Or is it? The perils of repurposing

- Bottom line Cost growth avoidance

- Why is this so difficult?

- Solutions and success strategies

### Raytheon Missile Systems

## "It's Just a Simple Upgrade..."

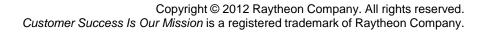

- Service life extensions present the need for obsolescence and other upgrades

- Upgrades are fraught with challenges

- Cost and schedule risks are common

Don't be trapped by "it is just a simple upgrade" — upgrades require real engineering discipline

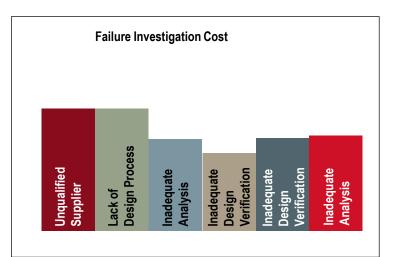

## The Perils of Repurposing

Too many assumptions about reuse can result in unintended consequences

Repurposing without proper planning, system thinking and engineering discipline creates failure

## **Do the Real Engineering**

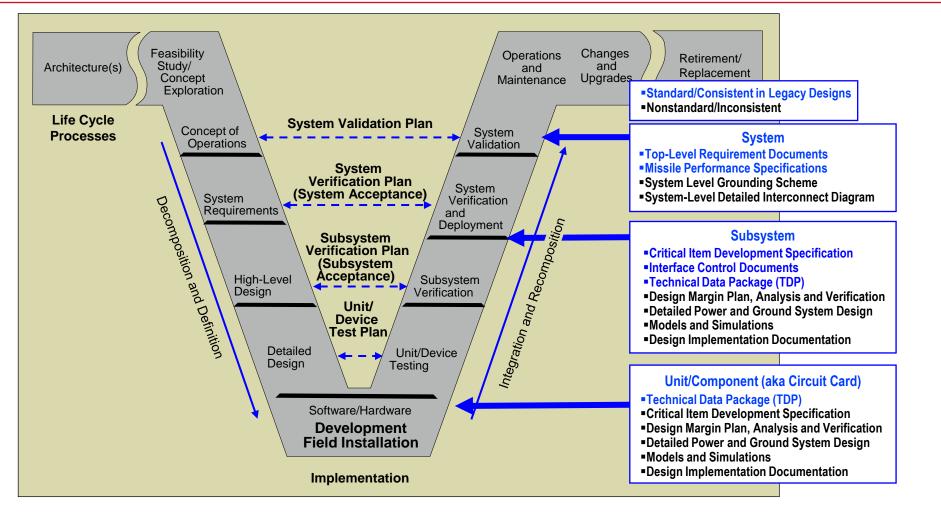

- Capability upgrades and obsolescence respins require true system engineering at the subsystem level

- Inclusive engineering needed to readdress associated design artifacts and avoid unpredictable execution

- Proper scoping of engineering effort can avoid many issues

Lack of sufficient subsystem engineering causes cost growth in obsolescence respins and upgrades

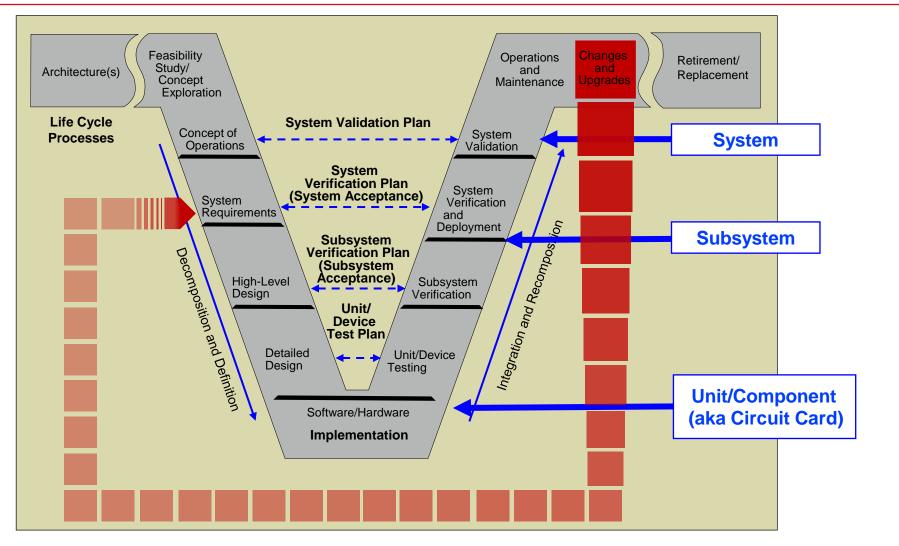

## System Life Cycle — "The V"

Changes and upgrades happen outside the normal development process

### Raytheon Missile Systems

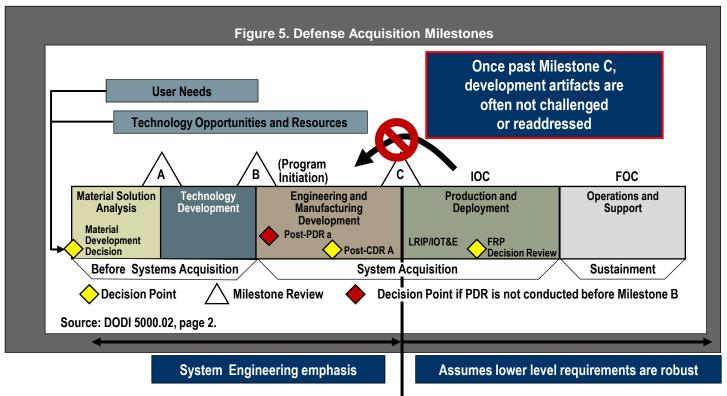

## **Acquisition Policy Impact**

- Post-acquisition reform DoD acquisition practices (capability-based acquisition) initially drove minimalistic subsystem engineering

- Current defense acquisition policy expects engineering rigor before Milestone C

DoD acquisition scheme expects system and subsystem engineering completion before Milestone C — not budgeted for later in the life cycle

## **Faulty Planning and Flawed Expectations**

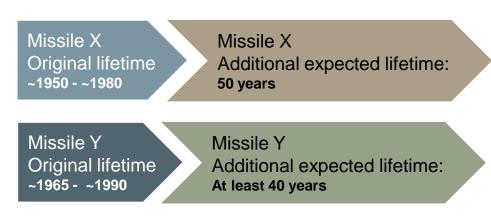

- Drivers of cost over-runs

- Flawed assumptions about readily available data or documentation

- Requirements of original design not fully understood or applicable

- Scope of replacement may grow after uncovering additional needs

- Engineering discipline required after Milestone C

- Upgrading a legacy capability based system may require going through some of the proper development process for the first time at the subsystem level

We can't afford to understate, sit on or cover up problems in any program — at any time — at any level. They must be brought forward. This includes not just "show stoppers" but also "show slowers." I can't stress this strongly enough [19:26].

(Former Under-Secretary of Defense for Acquisition, Donald J. Yockey)<sup>2</sup>

[including scope definition,]

Without more realistic estimates, ^ senior management may be lulled into a false sense of security about their programs and fail to take appropriate action to correct problems

~ An Analysis of Cost Overruns on Defense Acquisition Contracts<sup>2</sup>

"Faulty initial engineering plans and concepts are not the root of all cost growth, but are involved in much of it."<sup>3</sup>

## Why Is This So Difficult?

Legacy solutions may be incompatible with modern practices and component selections

#### Legacy/Modern Incompatibilities

Older systems were not designed with Modular Open System Architecture (MOSA) approach

Partitioning and interfaces may not easily accommodate modern interfaces

Accommodating legacy interfaces may in fact add complexity

Modern components with sufficient environmental requirements may not exist

Power system requirements — small changes may affect the whole power system

Modern devices with fast timing may require changes to grounding techniques or other interfacing components

Lack of documented requirements and implementation at the subsystem level

### Lack of Subsystem Engineering Artifacts

•Difficult to respin a single Circuit Card Assembly (CCA) for obsolescence without its set of detailed requirements

May spend a significant amount of time creating/documenting requirementsMissing implementation details hinders insight into original design choices

'Price to win' contract strategies force tradeoffs in the resources allocated to the Systems Engineering process during proposal and execution<sup>4</sup>

Cost and schedule constraints drive avoidance of robust re-qualification

Replacements have many constraints and drivers — "faster is not always better" — hence the need for real engineering discipline

## **Engineering Solutions**

- Two fundamental approaches to addressing unexpected issues during legacy system upgrades:

- Planning: Complete and comprehensive initial bid

| DS Process ID -<br>Builder | Task Name - Builder                                                | Typical<br>Duratio | Typical<br>Hours -<br>Builder | Predecessors -<br>Builder | Successors<br>- Build | Owner Org -<br>Builder 💂 | Performing Orgs (with weighting) - Builder | Oct '10<br>19 26 3 10 17 | Nov '10  | Dec '10  | Jan '11<br>26 2 9 16 23 |      | Mar '11<br>27 6 13 20 27 |

|----------------------------|--------------------------------------------------------------------|--------------------|-------------------------------|---------------------------|-----------------------|--------------------------|--------------------------------------------|--------------------------|----------|----------|-------------------------|------|--------------------------|

|                            | S4_AnalogCCA_PreDan                                                | 0 days             | 0 hrs                         |                           |                       |                          |                                            |                          |          |          |                         |      |                          |

|                            |                                                                    | 1 day?             | 0 hrs                         |                           |                       |                          |                                            | 1                        |          |          |                         |      |                          |

|                            | Advance Trade Studies and Requirements Completed - [CCAName] CCA   | 79 days?           | 596 hrs                       |                           |                       | ALEX                     |                                            | -                        | _        | _        |                         |      |                          |

|                            | Receive Unit Electrical Requirements - [UnitName] Unit             | 0 days?            | 0 hrs                         |                           | 7,5                   | ELXSUB                   |                                            | 4)10/7                   |          |          |                         |      |                          |

|                            | Receive Unit Mechanical requirements - [UnitName] Unit             | 0 days             | 0 hrs                         | 4                         | 6                     | ELXSUB                   |                                            | ++ 10/7                  |          |          |                         |      |                          |

| 3-05.01-03                 | Complete Advanced Concept Studies - [CCAName] CCA                  | 20 days            | 80 hrs                        | 5                         | 8                     | ALEX                     | AELX                                       | 4                        | <b>_</b> |          |                         |      |                          |

| 3-05.01-03                 | Complete Electrical Architecture trade study - [CCAName] CCA       | 20 days            | 80 hrs                        | 4                         | 8                     | ALEX                     | AELX                                       | <u> </u>                 |          |          |                         |      |                          |

|                            | Complete Electrical concept - [CCAName] CCA                        | 17 days            | 116 hrs                       | 6,7                       | 13                    | ALEX                     | ALEX                                       |                          | ÷—       | ₩i i     |                         |      |                          |

| ??                         | Review Lessons learned - [CCAName] CCA                             | 5 days             | 40 hrs                        |                           | 10                    | ALEX                     | AELX                                       |                          | -        |          |                         |      |                          |

| 3-05.01-03                 | Complete Electrical Architecture down select - [CCAName] - CCA     | 2 days             | 16 hrs                        | 9                         | 11                    | ALEX                     | AELX                                       |                          | ě,       |          |                         |      |                          |

| 3-05.01-03                 | Complete Preliminary Block diagrams - [CCAName] CCA                | 5 days             | 20 hrs                        | 10                        | 12                    | ALEX                     | AELX                                       |                          | <b>1</b> |          |                         |      |                          |

| 3-05.03                    | CCA Cost Assesment - [CCAName] CCA                                 | 5 days             | 40 hrs                        | 11                        |                       | ALEX                     | AELX                                       |                          |          |          |                         |      |                          |

|                            | Complete Verification Requirements - [CCAName] CCA                 | 22 days            | 80 hrs                        | 8                         | 20,21                 | ALEX                     | AELX                                       |                          |          | 4        | <b>•</b> 1              |      |                          |

| 3-05.02-01                 | Complete Preliminary Test Strategy                                 | 10 days            | 40 hrs                        |                           | 16                    | ALEX                     | AELX                                       |                          |          |          |                         |      |                          |

| 3-05.02-01                 | Complete Preliminary Testability & BIT Requirements                | 10 days            | 40 hrs                        |                           | 16                    | ALEX                     | AELX                                       |                          |          |          |                         |      |                          |

| 3-05.02-01                 | Complete Requirements Compliance Matrix                            | 3 days             | 0 hrs                         | 15,14                     | 17                    | ALEX                     | AELX                                       |                          |          | <b>1</b> |                         |      |                          |

| 3-05.02-01                 | Complete Draft DRD                                                 | 3 days             | 0 hrs                         | 16                        | 18                    | ALEX                     | AELX                                       |                          |          | ۵.       |                         |      |                          |

| 3-05.02-01                 | Complete DMA & identify initial KPC's                              | 3 days             | 0 hrs                         | 17                        | 19                    | ALEX                     | AELX                                       |                          |          | <u>ة</u> |                         |      |                          |

|                            | Perform Requirements Review DNA - [AnaCCAName] Analog CCA          | 3 days             | 0 hrs                         | 18                        |                       | ALEX                     | AELX                                       |                          |          | -        |                         |      |                          |

| 3-05.04                    | Complete Preliminary Electrical Models/Simulations - [CCAName] CC  | 20 days            | 120 hrs                       | 13                        | 22                    | ALEX                     | AELX                                       |                          |          |          |                         |      |                          |

| 3-05.04                    | Preliminary Thermal/Mechanical Models - [CCAName] CCA              | 20 days            | 120 hrs                       | 13                        | 22                    | ALEX                     | Mech                                       |                          |          |          | <u> </u>                |      |                          |

|                            | Deliver advance trade studies and requirements - [CCAName] CCA     | 0 days             | 0 hrs                         | 20,21                     |                       |                          |                                            |                          |          |          | *                       | 1/25 |                          |

|                            | * Advanced Design Review (ADR) Completed - [CCAName] CCA           | 21 days?           | 120 hrs                       |                           |                       | ELxC                     |                                            |                          |          |          |                         |      |                          |

|                            | Preliminary Design and Analysis Completed -[CCAName] CCA           | 120 days           | 1,072 hrs                     |                           |                       | ALEX                     |                                            | -                        | -        |          |                         |      | <b>—</b>                 |

|                            | Proliminary Test and Verification Planning Completed -[CCAName] CC | 45 days            | 260 hrs                       |                           |                       | ELxC                     |                                            |                          | -        |          |                         |      |                          |

|                            | Internal Preliminary Design Review Completed - [CCAName] CCA       | 21 days?           | 140 hrs                       |                           |                       |                          |                                            | _                        | _        |          |                         |      |                          |

Execution: Engineering at the subsystem level

Good systems engineering must extend down to subsystem level

## Planning Solutions — Complete a Comprehensive Initial Bid

Better tailoring and execution

- Higher fidelity plans: Avoid "quick and dirty" Rough Order of Magnitude (ROMs) that lack fidelity and consideration for all life-cycle aspects, but can set false expectations

- Thoughtful assumptions: Avoid "misuse of reuse" by determining availability of documented requirements and implementation, fabrication and test capability, and minimizing assumptions

- Prevent under-planning and ease execution by gaining a solid understanding of the leverage gained from reuse and industry standards (or lack thereof)

- A realistic and comprehensive plan will result in **flawless execution**

Plans must not sacrifice proper subsystem engineering

## Execution Solutions — Engineering at the Subsystem Level

Engineering integrity required to avoid later unintended consequences

Kavtheon

**Missile Systems**

- Engineering rigor will reduce multiple iterations, lowering cost

- To minimize iterations during respin or upgrade, ensure design integrity and compatibility with remaining system from the beginning

- Extra effort up front can eliminate one or more unexpected qualification or test failures late in the program

- Early investment in generation or modification of requirements, analysis, modeling and simulation, and verification activities can prevent escapes during later stages of the life cycle

- Documentation of requirements, analysis and results at all levels helps with knowledge transfer later in product life cycle

Subsystem engineering supports design integrity

## **Subsystem Engineering Specifics**

Critical subsystem artifacts need to be available or created for legacy systems

### **Detailed Strategies for Successful Upgrades**

Requirements must be product (subsystem) based

Trades must account for further future upgrades

#### System-Based Requirements Considerations

Flow environmental and other requirements to the level of the replacement

Fully understand and document the contribution of the subsystem to overall system performance

- •Comprehend the reasons behind legacy implementation to ensure necessary functionality/operation not negatively affected by the upgrade

- What requirements were waived or not met previously that should be met now?

- •What were initially implementation details became requirements when system was completed

### Subsystem Trade Considerations

- •Was modular open architecture implemented in legacy system? If not, can it be added and in what portion(s) of the system?

- •Can partitioning within the subsystem ease later obsolescence replacements?

- •Can an older technology be retained and sustained or must it be upgraded to something more available?

The devil is in the details

### **Detailed Strategies for Successful Upgrades**

Analyses must extend beyond subsystem to ensure full compatibility

#### **Subsystem Analysis Considerations**

- •Will implementation details of the replacement negatively affect surrounding subsystem (or vice-versa)?

- Can newer technologies directly interface with existing or are translations necessary?

- •Will the modification adversely affect power, grounding, software or other system aspect?

Models and simulations should be as high fidelity as possible

#### **Modeling and Simulation Considerations**

- •Do high-fidelity models and simulations exist or must they be created or upgraded?

- Readdressing the models and simulations forces engineers to think through the details of the upgrade and ensure nothing is missed

- •Leveraging existing higher fidelity models and simulations can save significant effort

# Models, simulations and analyses must be updated and validated

### **Detailed Strategies for Successful Upgrade**

Verification must be performed at all levels

#### **Verification Considerations**

- Design margin verification and delta design verification testing (DVT) must be completed

- •Qualification: What was done previously and how much "similarity" can be gained?

- •Model verification and validation: use test data to validate models

- •What failures occurred or deviations were requested during the original development effort?

### Test strategies must be considered from the beginning

### **Test Considerations**

- Planned test reduction for production programs may have eliminated equipment needed to verify a design spin

- Updated interfaces at lower levels of assembly may require modifications to existing test setups

- Reprogrammability and built-in test (BIT) should be designed in at every opportunity

- Initial data for statistical process control in the factory must start being collected during verification phase

- •Clear understanding of production line capabilities and availability is essential

Need detailed verification at lower levels to support higher-level operability and reliability

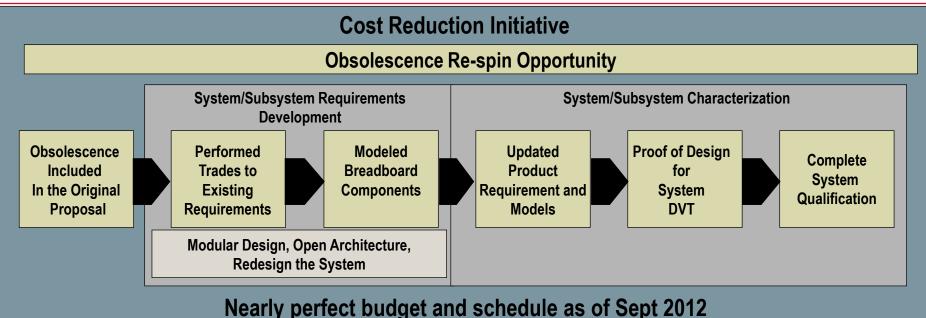

## Success Story

- Assumptions about availability of engineering artifacts validated

- Model Development and design verification well thought out and properly planned and executed

- System level EMI testing included

- Teamwork between the customer and the contractor to define a clear statement of work

- All of the legacy design documentation was reviewed for completeness and updated as necessary

- Customer is ecstatic with the performance

Proper planning strategy and engineering rigor help to keep cost under control even with a very aggressive schedule

## Summary

- **Don't be trapped** by "it is just a simple upgrade"

- The constraints and drivers of capability and obsolescence upgrades can result in cost-driven decisions that reduce subsystem engineering and ultimately add risk

- Subsystem design information required to efficiently and effectively replace portions of a system should be assumed as not available (validate those assumptions)

- Incorporating the outlined strategies will promote design integrity

- Subsystem engineering discipline and proper scoping of the effort will keep cost and schedule in check

Subsystem engineering discipline is a key to long term success Non-technical per ITAR 120.10(5)

# **Questions?**

## Bibliography

- COTS: Doing it Right; Jacques S. Gansler , Ph.D. <u>http://www.dtic.mil/cgi-</u> <u>bin/GetTRDoc?Location=U2&doc=GetTRDoc.pdf&AD=AD</u> <u>A494033</u>

- 2. Christensen, David S. 1993. "An Analysis of Cost Overruns on Defense Acquisition Contracts." *ProjectManagement Journal 3:43-48 (September).*

- 3. Cost Growth In Major Defense Acquisition: Is There A Problem? Is There A Solution? *William D. O'Neil*; July 2011

- National Defense Industrial Association Systems Engineering Division Task Group Report Top Systems Engineering Issues In US Defense Industry September 2010 (Final-v11-9/21/2010)

## **About the Authors**

- Milly Lierman is an Engineering Fellow with Raytheon Missile Systems and has 21 years of experience with Raytheon/Hughes Aircraft, having held various design and leadership roles in the Electronics Center and Electrical Subsystems Directorate (ESD). Currently she holds the position of product area lead for the Naval Area Mission Defense and part of Air and Missile Defense Systems product lines. This role allows her to work with various program leaders and customers, guiding technical work and helping teams to plan and execute within budget and on schedule. Lierman has a dual bachelor's degree in electrical and computer engineering from Purdue University and a master's degree in electrical engineering from the University of Arizona.

- Milly L. Lierman; Raytheon Missile Systems Company, 520.794.0448, mllierman@raytheon.com

- Tim Morrill is an Engineering Fellow in the Electronic Subsystems Design Directorate. He has been with Raytheon for 13 years. He was originally hired into the electronic controls design department. He was a section manager for seven years while he worked on various programs at RMS. Before Raytheon he worked for Delco Electronics in Kokomo, Ind. for five years. He was the electrical design lead for the four-wheel steering program that was integrated on the Denali line of SUVs. He worked for Hughes Aircraft Company in Las Vegas, Nev. for 10 years designing one-of-a-kind radar systems. Before working in the private industry, Morrill was enlisted in the USAF. Tim was an automatic tracking radar specialist and worked in the electronic warfare arena as a red force operator. Morrill's experience spans the entire life cycle of the product.

- Timothy G. Morrill; Raytheon Missile Systems Company, 520.663.9622, tgmorrill@raytheon.com