# L-3 Fuzing & Ordnance Systems 59<sup>th</sup> Annual Fuze Conference May 5, 2016

L-3 FUZING & ORDINANCE SYSTEMS

PUBLIC DOMAIN. This document consists of general capabilities information that is not defined as controlled technical data under

ITAR Part 120.10 or EAR Part 772.

# Quality Driven Complex Logic Development Process

May 3<sup>rd</sup>- 5<sup>th</sup>, 2016

**Open Session**

**Nick Adams**

L-3 FUZING & ORDNANCE SYSTEMS

PUBLIC DOMAIN. This document consists of general capabilities information that is not defined as controlled technical data under

ITAR Part 120.10 or EAR Part 772.

# **Objective and Exit Criteria**

#### Objective

Allow Groups an opportunity to understand the basic technical details of an FPGA, the overall development process and the specific design details that are undertaken by the L-3 FOS Complex Logic design team to provide a quality Complex Logic Device to our customer.

#### Exit Criteria

- Demonstrate an understanding of the FPGA complex logic component

- Demonstrate an understanding of the development process

- Demonstrate an understanding of the implementation methodology

# **Design Methodology**

Areas involved in the development of a complex logic design

- Project planning and tracking

- Tool selection in the EDA (Engineering Design Automation) space

- Source control, version control and configuration management mechanisms

- Requirement traceability

- Design strategy and criteria

- Verification methods and coverage metrics

- Validation goals and a release and life cycle management plan

"Do it Once ... Do it Right"

# **Background Information**

What is an FPGA?

#### An FPGA is **HARDWARE**.

- FPGA is a Field Programmable Gate Array

- It "IS" an Integrated Circuit

- It "IS NOT" Software

- It "IS" Programmed

- It "IS NOT" a program

FPGAs contain programmable components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together".

Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR.

In FPGAs, the logic blocks also include memory elements or registers.

# **Hardware Descriptive Language (HDL)**

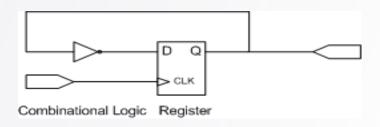

In integrated circuit design, Register Transfer Level (RTL) description is a way of describing the operation of a synchronous digital circuit.

Behavior is defined in terms of:

- Flow of signals (transfer of data) between hardware registers.

- Logical operations performed on those signals.

RTL abstraction is used in **HDL's** or **Hardware Description Languages** like **Verilog** to create high-level representations of a circuit, from which lower-level representations and ultimately actual wiring is derived.

FPGA's are programmed with HDL

```

assign D = ~Q;

always @ (posedge clk)

begin

Q <= D;

end</pre>

```

# **FPGA Design Methodology**

- FPGA design process utilizes a number of supporting procedures and guidelines to facilitate in the development of safe and reliable quality driven complex logic devices.

- These include company as well as project specific procedures and guidelines:

- FPGA Development Procedure

- FPGA Design Plan

- Development Checklist

- L-3 FOS RTL Coding Guidelines

- FPGA Directory Structure and Signal Naming Guidelines

- Internal Design Review Procedure

- Design Control Procedure

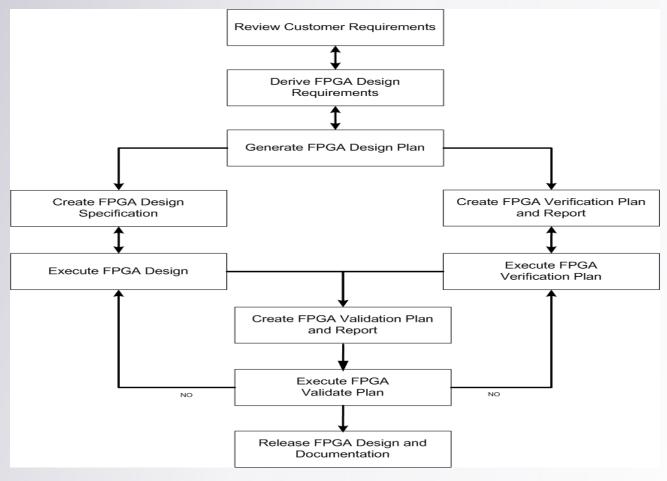

# **FPGA Design Process**

# **FPGA Development Reviews**

| Action                                      | Entrance Document                                           | Exit Document                                 | Responsible Engineer(s)    | Review           |  |

|---------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|----------------------------|------------------|--|

| Review Customer Requirements                | Drafted Customer Requirements                               | Baselined / Released Customer<br>Requirements | Lead Electrical Engineer   | SRR              |  |

|                                             | (SOW, ICD, EICD)                                            | (SOW, ICD, EICD)                              |                            |                  |  |

| Derive FPGA Design Requirements             | Baselined Customer Requirements                             | FPGA Design Requirements                      | Lead Electrical Engineer   | IDR              |  |

| Generate FPGA Design Plan<br>(optional)     | Baselined / Released Customer<br>Requirements               | FPGA Design Plan                              | Engineering Manager        | FPGA Team Review |  |

| Create FPGA Design Description              | FPGA Design Requirements                                    | FPGA Design Description                       | FPGA Design Engineer       | IDR              |  |

| Create FPGA Verification Plan and<br>Report | FPGA Design Requirements                                    | FPGA Verification Plan and Report             | FPGA Verification Engineer | IDR              |  |

| Create FPGA Validation Plan and<br>Report   | FPGA Design Requirements  FPGA Verification Plan and Report | FPGA Validation Plan and Report               | Lead Electrical Engineer   | IDR              |  |

| Release FPGA Documentation Package          | FPGA Validation Plan and Report                             | FPGA Design File                              | Lead Electrical            | IDR              |  |

# **FPGA Project Tracking**

| Project: <####>               | Charge Number:       | Project Type:<br>Choose item |                  |              |

|-------------------------------|----------------------|------------------------------|------------------|--------------|

| Complex Logic Development Re  |                      | Sign Off when c              | ompleted         |              |

| Drawing Title:                | Number and Revision: | Author:                      | Review Sign-off: | Status       |

| FPGA Requirements             | <####>               |                              |                  | Completed    |

| FPGA Design Description       | <####>               |                              |                  | Choose item. |

| FPGA Verification Plan/Report | <####>               |                              |                  | Choose item. |

| FPGA Programmed Part          | <####>               |                              |                  | Choose item. |

| FPGA Label                    | <####>               |                              |                  | Choose item. |

| FPGA Programming File         | <####>               |                              |                  | Choose item. |

| FPGA Design Files             | <####>               |                              |                  | Choose item. |

| FPGA Validation Plan          | <####>               |                              |                  | Choose item. |

| FPGA Validation Report        | <####>               |                              |                  | Choose item. |

| FPGA Requirements Review                                                                  | Date:       | Click here to enter a date. |

|-------------------------------------------------------------------------------------------|-------------|-----------------------------|

| Checklist Item                                                                            | Response    | Comments                    |

| Is the Customer Specification referenced?                                                 | YES         |                             |

| Is this a single or multiple FPGA Design?                                                 | Choose item |                             |

| Has a maximum FPGA resource utilization been specified?                                   | Choose item |                             |

| Is the target FPGA package/device/technology specified?                                   | Choose item |                             |

| Is the target FPGA Grade (Commercial/Industrial/Military) or temperature range specified? | Choose item |                             |

| Is the design input method specified (schematic or HDL)?                                  | Choose item |                             |

# **FPGA Design Requirements**

- Project begins with Customer Requirements

- Externally supplied document for consumption by design team

- Reviewed by design team; First release point once accepted

- FPGA design requirements come directly from customer requirements

#### FPGA Design Requirements

- Gated by Customer Requirements

- High level requirements document incorporating [REQ\_TAG\_ID]

- "What" does the FPGA need to accomplish in the system

- "What" are the constraints

- "What" are the inputs and how do they behave

- "What" are the outputs and how should they behave

- Reviewed by design team; First release point once accepted

- Risks understood and assessed for all TBD's

# **FPGA Design Plan**

- Project management resource

- Defines people, methods and strategies to be implemented

- Scope and Schedule

- Team members and responsibilities

- Entrance and exit criteria

- Meeting and review procedures

- Status and progress reporting practices

- Issue / Bug reporting and tracking

- Methods, tools and conventions utilized

# **FPGA** Design Description

- Gated by FPGA Design Requirements

- Details "How" the design requirements will be met in hardware

- Describes device architecture

- Defines structural blocks functions and interfaces

- Reviewed by design team; First release point once accepted

# **FPGA Design Strategy**

Independence

Maintained

Between Design

&

Verification

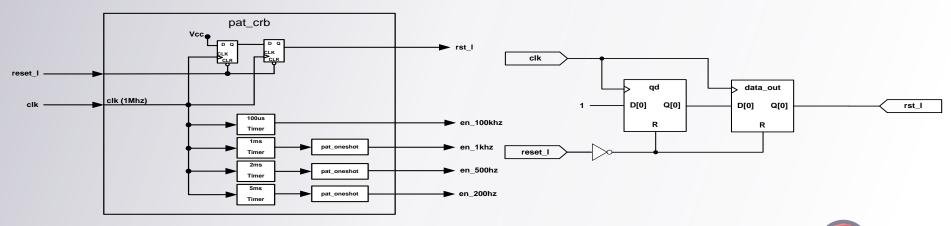

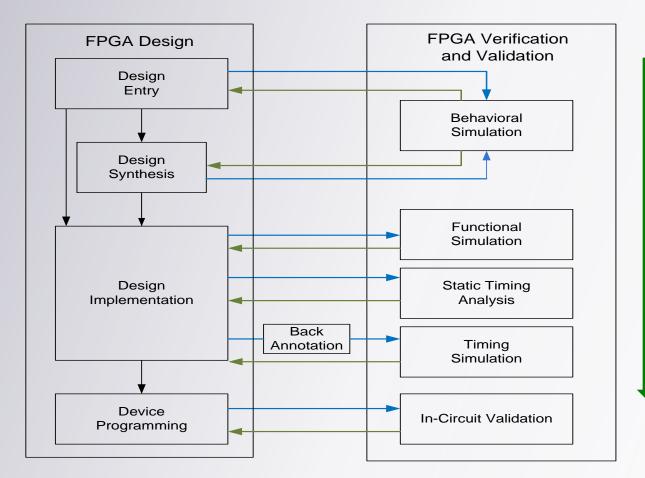

# **FPGA Design Execution**

- Design execution and verification typically run in parallel

- Design Execution includes:

- Logic partitioning

- Design Entry

- Design Synthesis

- Block level verification

- Design implementation

- Device programming

- Design ensures hardware implements defined requirements

- Verification ensures hardware meets derived requirements

- Verification and Validation

- Verification is 100% functional coverage done in EDA environment

- Validation is a subset of Verification done in hardware

- Not all verification points can be realized in hardware

#### **Verification Plan**

- Design verification analyzes a design for proper performance and function as defined in the Architecture Specification.

- Performed repeatedly during design development.

- Ensures that the building blocks exhibit required behaviors and then that the entire design exhibits the required behaviors.

- Done in an EDA environment not in hardware.

(when we hit hardware we have entered Validation).

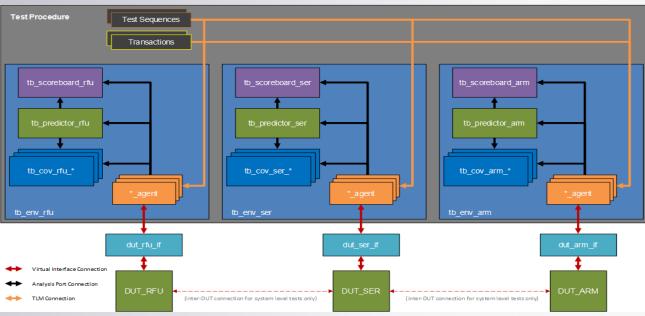

# FPGA Verification: Simulation Environment

- Universal Verification Methodology (UVM) version 1.2

- Questa 10.4a simulator

- Separate simulation environments for each FPGA, and a combined simulation environment with all three FPGAs connected together

- Full code coverage and functional coverage collection with links to FPGA requirements document

#### **FPGA Verification**

- FPGA Verification Test Plan and Report document contains inspection and simulation test cases identify the requirements that are being verified, the stimulus that is being performed, and the expected behavior of the FPGAs

- Simulation test environment is also documented in the verification test plan and report

- Verilog designs are linted as part of the verification

- Functional Covergroups are used to ensure all simulation test case stimulus and conditions are simulated

- Verilog Code Coverage metrics are captured to ensure the design is tested

- Synthesis and Layout configuration and log files are inspected to verify the FPGAs meet timing, have the correct pin-out, device selection, etc.

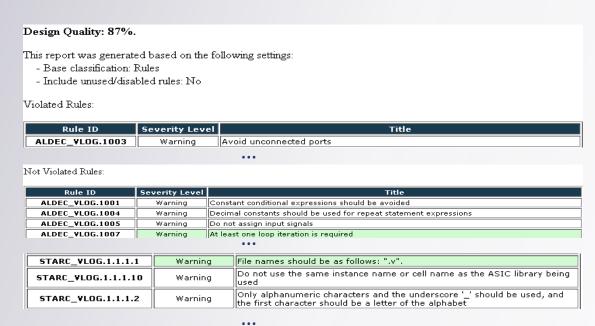

# Verilog Linting with Aldec's ALINT

- ALINT is a design rule checking software that is used to identify coding style, functional, and structural problems that are difficult to debug in simulators and in hardware

- FPGA designs are "linted" early in the development as part of the design verification

- Target Goal:100% Design Quality (Info, Warning, Critical Warning and Error Free).

# **FPGA Code Coverage**

| erage Report Totals BY FILE | S: Number o | f Files 4 | 1      |          |        |

|-----------------------------|-------------|-----------|--------|----------|--------|

| Enabled Coverage            | Active      | Hits      | Misses | Weight & | Covere |

| Stmts                       | 1726        | 1641      | 85     | 1        | 95.    |

| Branches                    | 1540        | 1453      | 87     | 1        | 94.    |

| Conditions                  |             |           |        | 1        | 84.    |

| UDP Condition Rows          | 0           | 0         | 0      | 1        | 100.   |

| FEC Condition Terms         | 500         | 341       | 159    | 1        | 68.    |

| Expressions                 |             |           |        | 1        | 88.    |

| UDP Expression Rows         | 0           | 0         | 0      | 1        | 100.   |

| FEC Expression Terms        | 301         | 234       | 67     | 1        | 77.    |

| FSMs                        |             |           |        | 1        | 94.    |

| States                      | 116         | 113       | 3      | 1        | 97.    |

| Transitions                 | 158         | 144       | 14     | 1        | 91.    |

Total coverage (Code Coverage Only, filtered view): 85.9%

|Total coverage \( \triangle \) | Stmt \( \triangle \) | Stmt graph | Branch \( \triangle \) | Branch \( \triangle \) | State \( \triangle \) | State \( \triangle \) | Transition \( \triangle \) | Transition \( \triangle \) | FEC Condition \( \triangle \) | FEC Expression \( \triangle \) | FEC Expression \( \triangle \) | FEC Expression \( \triangle \) | Transition \( \triangle \) | Transit ▼ Instance =-■ top dkgen\_arm \_\_\_\_ dkgen\_ser 🖃 🗾 dut\_arm 100.0% 90.0% 100.0% 99.6% 95.2% 100% 96.3% 97.7% 100% \_\_\_ dut\_ser 82.2% 93.7% 92.4% 96.2% 59.6% 91.1% 97.9% 98.7% 100% 100.0% 100.0% 100% 89.8% ±- ■ scb 50% 45.2% 62.0% 82.2% 76.5%

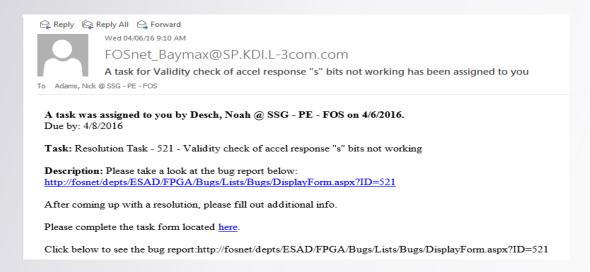

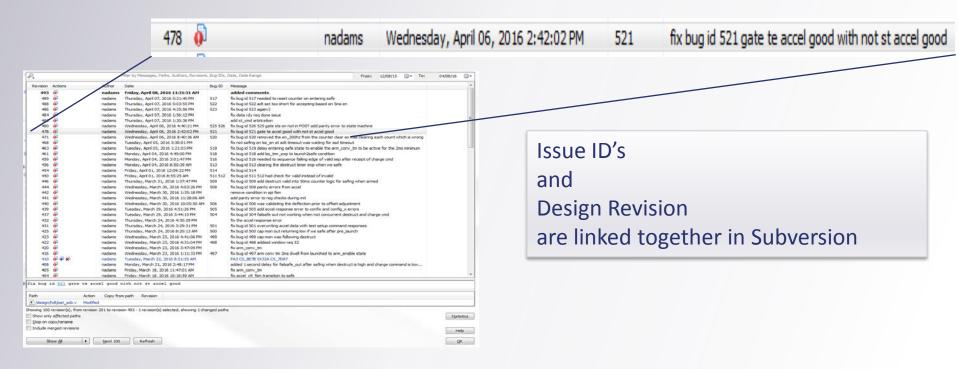

# **Issue Tracking and Revision Control**

#### SharePoint Issue Opened

#### Issue is assigned a unique ID

#### **Subversion Revision Control**

Issue fixed, design updated and committed into subversion repository for verification

# **SharePoint Issue Tracking**

Issue resolved, committed in subversion project repository and reassigned to be verified and closed

fixed in revision 478 gate te accel good with not st accel good FOSNet > ESAD Engineering > FPGA > Bug Database > Bugs Validity check of accel response "s" bits not working Bug Categories Validity check of accel response "s" bits not working ACTIONS Title. D3749 PATRIOT Project » Add a Project Category Active BY ASSIGNMENT Assigned to Me Opened by Me Repro Steps Unassigned Bugs FPGA is in test-mode-enabled, and accel is in self-test-enabled, so proper s-bits are 2'b10. All Bugs Design Revision is Accel sample at 10062ms has wrong S-bits (2'b00), but integrator runs Recycle Bin Safety Critical All Site Content (2) Normal Severity Priority captured in Issue Desch, Noah @ SSG - PE - FOS Assigned To Resolution **Resolution Comment** Resolved By Adams, Nick @ SSG - PE - FOS 04/08/2016, 04:00 AM Resolution Due Date fixed in revision 478 gate te accel good with not st accel g Resolution Comments **Duplicate Bug** Related Bugs Verified By 2016-04-13704-00:002 Verification Due Date Verification Comments

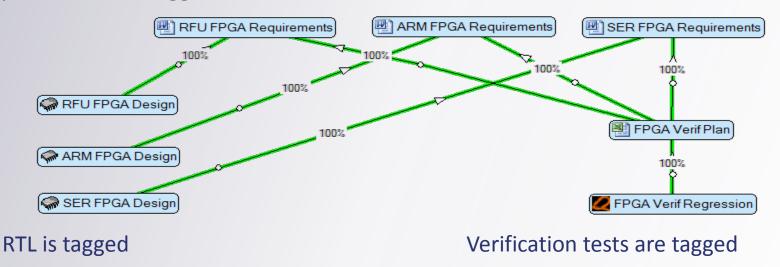

# **Requirement Traceability**

# **ReqTracer from Mentor Graphics**

Requirements are tagged

Tags in Requirements, Verification and Design are all linked together

### **FPGA Documentation**

#### FPGA Package Includes:

| Description                                |  |

|--------------------------------------------|--|

| FPGA Programmed Part                       |  |

| FPGA Label                                 |  |

| FPGA Fuse File                             |  |

| FPGA Electronic Design & Verification File |  |

| FPGA Design Requirements                   |  |

| FPGA Design Description                    |  |

| FPGA Verification Test Plan & Report       |  |

| FPGA Validation Plan & Report              |  |

#### Conclusion

The end result is a complex logic design process that approaches or is equivalent to a CMMI (Capability Maturity Model Integration) Maturity level 4, Quantitatively Managed, for product development.

CMMI is a process appraisal program and service required by many DoD and U.S. Government contracts applying to firmware and hardware development for complex logic devices.

#### **Contact Information**

# L-3 Fuzing & Ordnance Systems

Business Development Department 3975 McMann Road Cincinnati, Ohio 45245 513-943-2000