# **Optimizing Semiconductor Manufacturing with MBSE**

By Chris Howard

Presented by Steven Dam

#### Table of contents

01

Introduction

Background Information.

03

**Implementation**

Execution of improvement methods.

02

**Project Scope**

How can MBSE improve our project.

04

**Summary & Conclusion**

Different in operations before and after the project.

2

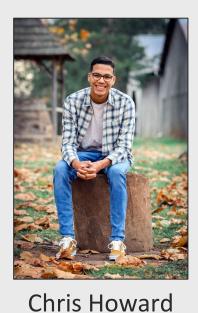

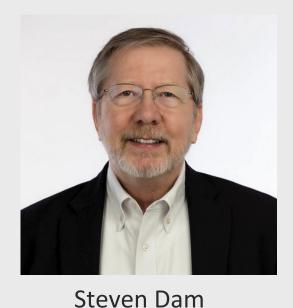

#### **Author & Presenter**

chrishoward@vt.edu

Computer Engineering

Student @VT

steven.dam@specinnovations.com

President of Spec Innovations

01

### Introduction

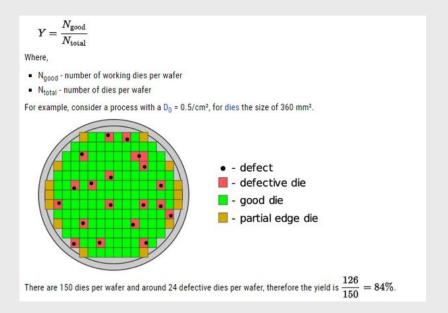

### Chip Manufacturing Yield - What is it?

5

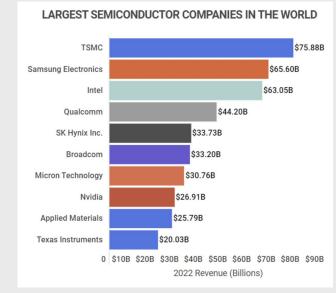

### **Key Findings**

- TSMC (Taiwan Semiconductor Manufacturing Company) has best target model.

- Revenue Impact: Higher Yield Rates correlate to significant revenue boosts.

- Cost Reduction: Lower loss can result in price-per-unit manufacturing to drop by 20%.

- Efficiency: If cost per unit is reduced, overall efficiency increases, as less material is wasted.

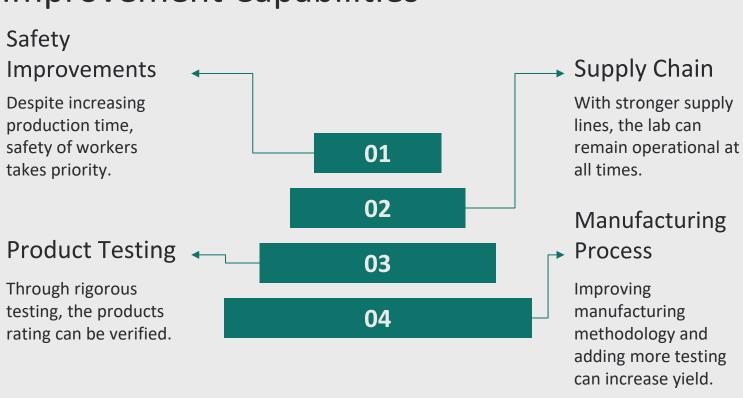

## Project Scope

### Improvement Capabilities

8

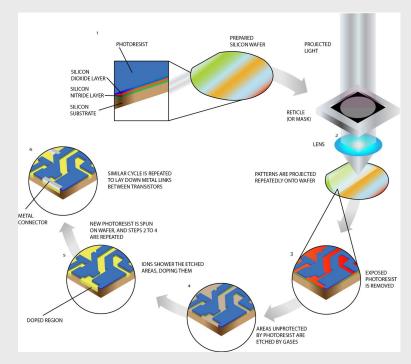

### Manufacturing Process - High Level

Let's get a quick visual of the chip manufacturing process.

Keep in mind that this is extremely high level, with much information cut.

$From\ gallagherse als. com$

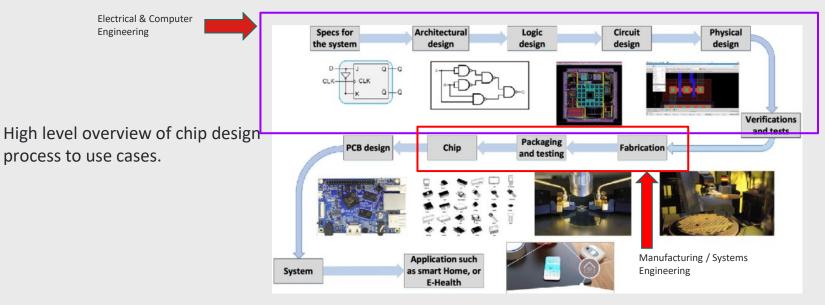

### Manufacturing Process - Use Cases

From researchgate.net

### Implementation

11

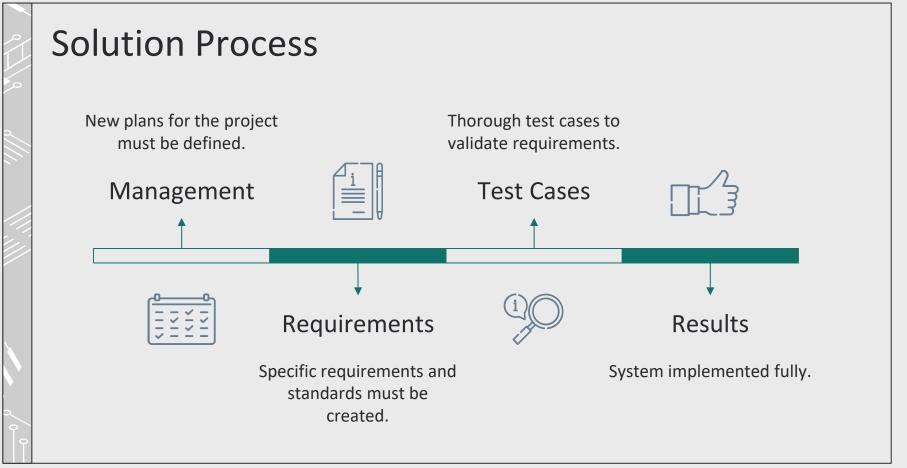

#### **MBSE Methods**

#### Diagrams

Diagrams are used in order to model actions, which can consume time or resources previously allocated.

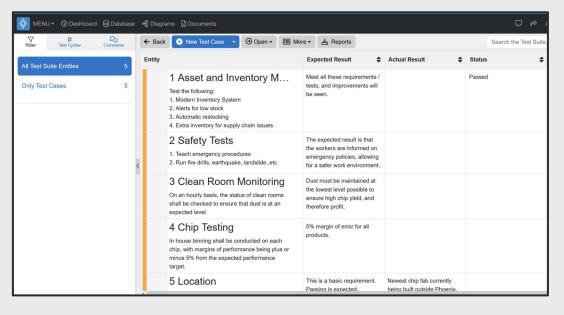

#### **Test Cases**

Test cases can be directly linked to requirements or actions to validate them.

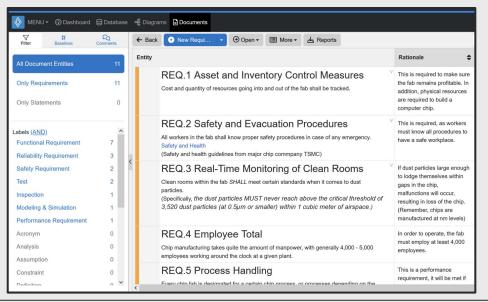

#### Requirements

Similar to most systems engineering, requirements are paramount and can also be modeled in MBSE.

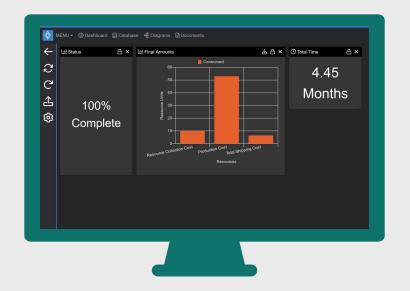

#### Management Overview

Gives an overview of the current progress of the project, allowing management to stay in tune with the status.

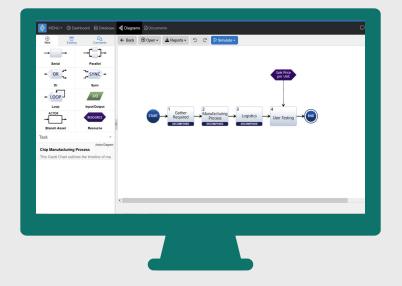

# Diagrams

### **Action Diagram**

By creating actions with specified lengths, resource consumption values, and ID's, specific actions and their impact on the system can be tracked.

Overall, diagrams allow stakeholders outside the project have a high level idea of the process of activities.

Simulations are also an option to show the projected result of a project.

### **Current Operation**

Currently, using fail conditions at given percentage values according to historical data, we can estimate the chance of processes being repeated.

This will result in an increased amount of time and resources spent to manufacture the chip.

### **Current Operation**

Current Simulation Data:

Time: 4.45 months

Resource Collection Cost: 10

Production Cost: 53

Shipping Cost: 7

Total: 70

# Requirements

### Requirement Usage

- Following the "V-Model" we initially declare requirements

- Clearly defines demands of the project

#### **Test Cases**

- Test Cases verify requirements

- Mandatory to a successful system

### Traceability Matrix

Allows us to have a clear visual of the requirements being verified by tests.

|                                   |   | at an  | dinent | ory Man? | on Mon   | tocs Locs |

|-----------------------------------|---|--------|--------|----------|----------|-----------|

| MAN Comment Oble 5-1 Possible     |   | 255° 2 | Safe 3 | cies. V  | child 51 | ,oc       |

| MAIN Computer Chip Fab Requirem   |   |        |        |          |          |           |

| REQ.1 Asset and Inventory Control | X |        |        |          |          |           |

| REQ.2 Safety and Evacuation Proc  |   | X      |        |          |          |           |

| REQ.3 Real-Time Monitoring of Cle |   |        | X      |          |          |           |

| REQ.4 Employee Total              |   |        |        |          |          |           |

| REQ.5 Process Handling            |   |        |        |          |          |           |

| REQ.5.1 Process Handling Informat |   |        |        |          |          |           |

| REQ.6 Chip Testing                |   |        |        | X        |          |           |

| REQ.6.1 Methodology               |   |        |        |          |          |           |

| REQ.7 Shipping                    |   |        |        |          |          |           |

| REQ.8 Location                    |   |        |        |          | X        |           |

| PEO 9.4 Construction Quality      |   |        |        |          |          | ~         |

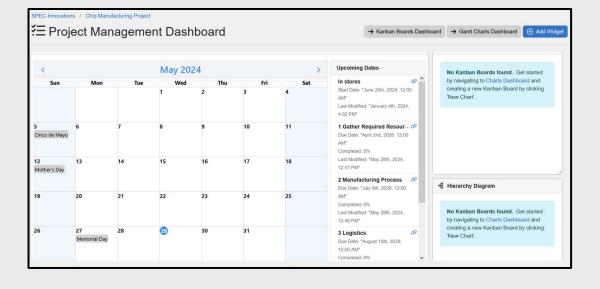

### Management View

Allows project stakeholders to view overall progress of project in a high level overview.

# Summary & Conclusion

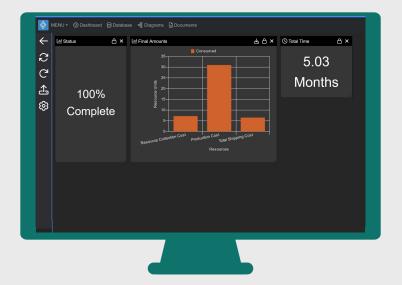

### **New Operations**

New Simulation Data:

Time: 5.03 months

Resource Collection Cost: 7.20

Production Cost: 31

Shipping Cost: 7

Total: 45.20

35% reduction in production cost / 35% improvement in yield.

10% increase in production time with extra tests

#### Takeaway:

To sum up, MBSE can be employed in order to provide organized testing and resource tracking in order to improve chip yield, which leads to higher profit and relevance in the industry,

# Questions?